Mastering PCB Solder Mask and Silkscreen Design to Avoid Manufacturing Defects

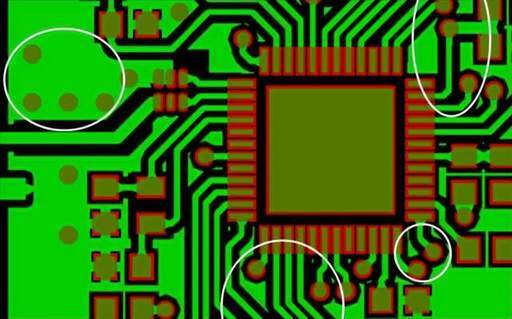

In the realm of electronics manufacturing, the solder mask and silkscreen layers do much more than provide aesthetics; they are fundamental to soldering precision, production yield, and post-assembly testing. Poorly executed PCB solder mask and silkscreen design can lead to critical failures such as "mask on pad," solder bridging, blurred component identifiers, or missing polarity markers. As high-density and multi-layer boards become the industry standard, adhering to strict Design for Manufacturing (DFM) principles is no longer optional.

This guide explores the most common pitfalls in PCB solder mask and silkscreen design and provides professional recommendations to help engineers lower production risks and ensure a high first-pass yield.

I. Solder Mask Design: Precision and Protection

The solder mask (or solder resist) is the protective coating that prevents solder bridges between closely spaced pads.

1. Inconsistency Between Via Tenting and Gerber Data

Problem: The design file (Gerber) shows via openings, but the manufacturing order specifies "Via Tenting" (covering).

Risk: This mismatch leads to fabrication delays or incorrect via processing, potentially causing exposed copper or solder drainage issues.

DFM Suggestion: Ensure your via opening settings in the CAD software are perfectly synchronized with your manufacturing order specifications.

2. Missing Solder Mask Openings on Functional Pads

Problem: Conducting pads are present on the copper layer, but no opening is defined on the mask layer.

Risk: "Mask on pad" prevents electrical contact, making it impossible to solder components.

DFM Suggestion: Every pad intended for soldering must have a mask opening. We recommend a "Solder Mask Expansion" of 0.05mm to 0.1mm to account for machine registration tolerances.

3. Excessive Solder Lines

Problem: Clearance lines in the solder mask are designed with excessive length or width.

Risk: Overly large clearances can lead to unintended copper exposure, increasing the risk of oxidation or shorts during the assembly process.

II. Silkscreen Design: Clarity and Identification

The silkscreen layer provides the essential "map" for manual and automated assembly.

1. Overlapping Silkscreen on Pads

Problem: Component outlines or text characters overlap with copper pads.

Risk: Manufacturers will "clip" (remove) any silkscreen on pads to ensure solderability, which often makes the remaining characters illegible.

DFM Suggestion: Maintain a safety clearance of at least 0.2mm between any silkscreen element and the edge of a solder mask opening.

2. Miniature Text Dimensions

Problem: Designing text that is too small for the printing process (inkjet or LPI).

Risk: The ink may bleed or fail to adhere, resulting in unreadable "smudges."

DFM Suggestion: Follow the "30/5 Rule": Use a minimum character height of 30 mil (0.76mm) and a minimum line width of 5 mil (0.13mm).

3. Hidden or Obscured Polarity Markers

Problem: Hiding polarity dots (for ICs) or stripes (for diodes) under component bodies or too close to pads.

Risk: Assembly technicians or AOI (Automated Optical Inspection) machines cannot verify component orientation, leading to functional failure.

DFM Suggestion: Place markers where they remain visible after the component is soldered, keeping a clearance of 0.2mm to 0.3mm from the pads.

III. DFM Reference Table for Professional Design

To achieve a reliable PCB solder mask and silkscreen design, use the following parameters as your baseline:

Conclusion

A successful PCB solder mask and silkscreen design is the result of balancing component density with manufacturing limits. By implementing strict DRC (Design Rule Check) routines for mask expansion and silkscreen clearance, you eliminate the most common causes of production delays. For engineers who prioritize reliability, PCBGOGO provides a full suite of DFM review services, specializing in optimizing solder mask and silkscreen layers to ensure your boards are not only functional but also easy to assemble and maintain.