High-Speed PCB Power Integrity Handbook: Ripple Reduction & Stability Optimization

1. Introduction

Power integrity (PI) is a decisive factor in the stability of high-speed digital systems. As signal rates surpass 10 Gbps, the allowable power ripple and noise margin have tightened to under 5%. Industry data shows that over 40% of high-speed PCB failures originate from power integrity issues. One AIoT manufacturer reported power ripple exceeding 20%, resulting in a 15% communication bit-error rate and delaying product launch by three months.

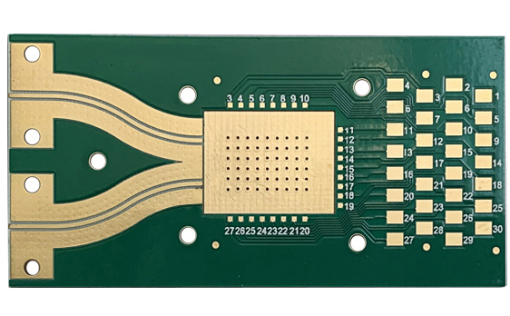

PCBGOGO has long specialized in high-speed PCB fabrication, offering a complete “PDN Design Optimization + Precision Manufacturing + Comprehensive Testing” solution. Its 6-layer high-frequency PCBs and 10-layer 2-step HDI products have been adopted by Hikvision, Dahua, and other top-tier brands.

This guide—based on IPC-2221 and IPC-6012—breaks down the core design principles and actionable steps required to achieve up to 80% ripple reduction in high-speed PCB power integrity.

2. Technical Foundations: Key Principles Driving Power Integrity

2.1 What Is Power Integrity?

Power integrity refers to the ability of the power delivery system to provide clean, stable power to ICs. Key PI indicators include:

Power ripple: ≤5%

Noise: ≤100 mV

Voltage regulation: ±2%

High-speed ICs experience transient current swings up to 1 A/ns. When PDN impedance is high, these transients generate voltage droop following ΔV = I × Z, leading to logic errors or instability.

2.2 Factors Affecting Power Integrity

PDN impedance is determined by the combined impedance of the:

Power plane

Ground plane

Vias

Decoupling capacitors

The target is to keep overall impedance below design limits (e.g., 1 Ω @ 100 MHz).

Other important factors include capacitor ESR/ESL, dielectric constant stability, plane-to-plane spacing, and via layout. IPC-2221 recommends a ≤0.2 mm spacing between power and ground planes to enhance coupling and reduce plane impedance.

2.3 PCBGOGO’s Process-Level PI Assurance

PCBGOGO enhances power integrity through three core manufacturing advantages:

High-precision LDI: XinJie LDI exposure ensures copper thickness uniformity within ±10%, minimizing power plane impedance deviation.

Optimized via drilling: Vega 6-axis drill machines maintain ±0.01 mm tolerance, reducing via impedance.

Comprehensive testing: The LC-TDR20 impedance analyzer verifies PDN impedance with 100% compliance.

3. Practical Workflow: Step-by-Step High-Speed PI Optimization

3.1 Define PDN Target Impedance & Run Simulations

Key steps:

Define target impedance based on IC transient current requirements and validate using simulation tools.

Formula:

Z<sub>target</sub> = ΔV / I<sub>peak</sub>

Where ΔV ≤ 5% × VDD.

Example:

3.3 V rail

I<sub>peak</sub> = 1 A

ΔV = 0.165 V

Target impedance ≤ 0.165 Ω @ 100 MHz

Recommended tools:

Cadence PDN Analyst 2023, ANSYS SIwave, IC datasheets from Intel/AMD.

3.2 Power & Ground Plane Design

Key steps:

Use tightly coupled “power–ground” adjacent layers to minimize spreading inductance.

Design standards:

Plane spacing: ≤0.2 mm (recommended 0.1–0.15 mm; IPC-2221 6.3.2 compliant)

Avoid large voids; if necessary, slot width ≤5 mm with stitching capacitors nearby

Copper thickness: ≥1 oz (2 oz for high-current sections)

Materials:

Isola/ Shengyi S1130 (Dk 4.3 ± 0.2)

3.3 Decoupling Capacitor Selection & Placement

Key steps:

Use multi-frequency decoupling with shortest possible current loops.

Recommended capacitor stack:

| Frequency Band | Capacitor Type | Specs |

|---|---|---|

| 1–10 kHz | Electrolytic | 10 μF, ESR ≤ 1 Ω |

| 10 kHz–1 MHz | Tantalum | 1 μF, ESR ≤ 0.1 Ω |

| 1 MHz–1 GHz | Ceramic | 0.1 μF, ESR ≤ 0.01 Ω |

Placement standards:

Capacitor to IC power pin distance: ≤5 mm

Via-to-pad distance: ≤2 mm (IPC-7351 compliant)

Brands: Murata, TDK

3.4 Via Optimization & Power Routing

Key steps:

Minimize via inductance and ensure routing supports required current.

Design standards:

Via diameter ≥ 0.3 mm

Each power pin: ≥2 vias

Via spacing: ≤4 mm

Power trace width: 1 mm per 1 A (1 oz copper)

Use 45° angles to avoid current crowding

Via copper plating: ≥25 μm (IPC-6012 compliant)

Tools:

Altium current-carrying calculator, PCBGOGO via capability table.

4. Summary

The heart of high-speed PCB power integrity lies in:

Accurately defining PDN target impedance

Optimizing the entire PDN chain (plane design, vias, decoupling, routing)

Leveraging high-precision manufacturing to ensure the design performs as intended

Simulation-driven design, frequency-matched decoupling, and tight plane coupling are essential to achieving stable performance and minimizing ripple.

5. Why PCBGOGO Is Your Best Partner for High-Speed PI Control

PCBGOGO offers comprehensive engineering and manufacturing support:

Built-in PI/PDN design rule checker in its online ERP ordering system

50+ senior engineers providing 1-on-1 simulation and design consultation

High-precision fabrication with advanced drilling, LDI, and impedance testing

Free prototypes for 1–6 layer high-speed PCBs—ideal for validating PI performance

Premium materials such as Shengyi and Rogers; mass production from 390 RMB/m2 for 4-layer boards with free shipping across six provinces

For future designs demanding higher current and lower noise, PCBGOGO’s thick-copper PCBs and HDI technologies offer greater via density and tighter copper-thickness control—further enhancing power integrity performance.